High-speed 1T 8051-based Flash MCU, 384 bytes SRAM, 8 Kbytes Flash, 128 bytes independent EEPROM, 16-channel dual mode touch circuit, 4-channel 8-bit PWM, 3 Timer/Counters, SSI, CheckSum module

# 1 General Description

The SC92F8372/8371/8370 (hereinafter referred to as SC92F837X) is an enhanced ultra-high speed 1T 8051 core industrial level integrated touch button function Flash micro controller, command system is fully compatible with the traditional 8051 product series.

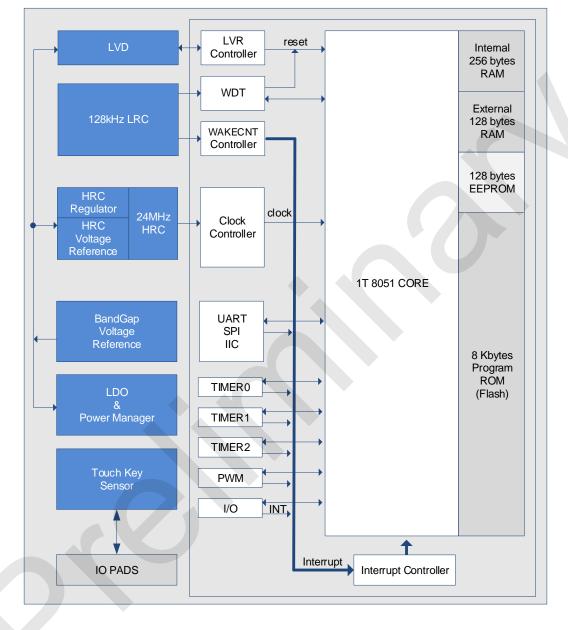

SC92F837X has a 16-channel, low-power, dualmode capacitance touch circuit that can be selected to run in STOP Mode. SC92F837X is integrated with 8 K Bytes Flash ROM, 384 Bytes SRAM, 128 Bytes EEPROM, up to 18 GP I/O, 7 IO external interrupts, 3 16-bit timers, 4 total cycles, duty cycle adjustable PWM, internal 1% high precision high frequency 12/6/2MHz oscillator and 4% precision low frequency 128K oscillator, a UART/SPI/IIC three choice a random SSI and other resources. In order to improve the reliability and simplify the customer circuit, SC92F837X is also integrated with 4 levels of optional voltage LVR and other high reliability circuits. anti-interference SC92F837X excellent has performance and excellent touch button performance, which is very suitable for various applications of touch button and master control, such as the size of smart home appliances and smart home, Internet of things, wireless communication, game consoles and other industrial control and consumer applications.

# 2 features

**Operating Voltage:** 2.4V ~ 5.5V

**Operating Temperature:** -40 ~ 85°C

### Package:

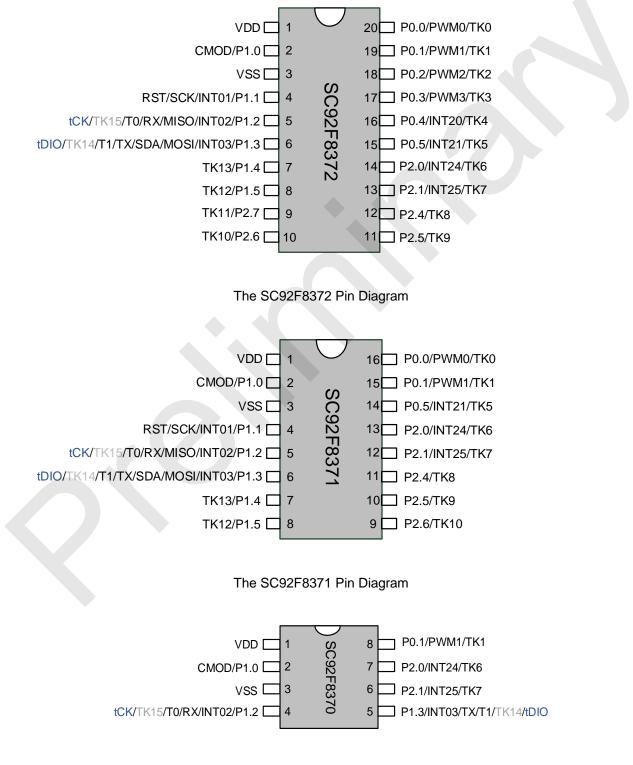

SC92F8372 (SOP20/TSSOP20) SC92F8371 (SOP16) SC92F8370 (SOP8)

Core: Ultra-speed 1T 8051

Flash ROM: 8 Kbytes Flash ROM (MOVC prohibited

Page 1 of 123

addressing 0000H~00FFH) can be rewritten 10,000 times

IAP: Code option into 0K, 0.5K, 1K or 8K

**EEPROM:** 128 bytes EEPROM can be rewritten 100,000 times. The data written-in has more than 10-year preservation life.

**SRAM:** Internal 256 bytes + external 128 bytes

System Clock (f<sub>SYS</sub>):

- Built-in 24 MHz high-speed RC oscillator (fHRC):

- as a system clock source, f<sub>SYS</sub> can choose set by programmer for 12/6/2 MHz

- Frequency Error: Suitable for 2.9V ~ 5.5V and -20 ~ 85°C application environment, no more than ±1%

### Built-in 128 kHz LRC Low-speed Oscillator:

- Available to act as clock source of Base Timer (BTM), which can wake up STOP

- Available to act as clock source of WDT

- Frequency Error: 4.0V ~ 5.5V and -20 ~ 85°C application environment, no more than ±4% of frequency error after register correction

#### Low-voltage Reset (LVR):

- 4-level LVR voltage options: 4.3V, 3.7V, 2.9V, 2.3V

- The default is the Code Option value selected by the user

### Flash Programming and Emulation:

• 2-wire JTAG programming and emulation interface

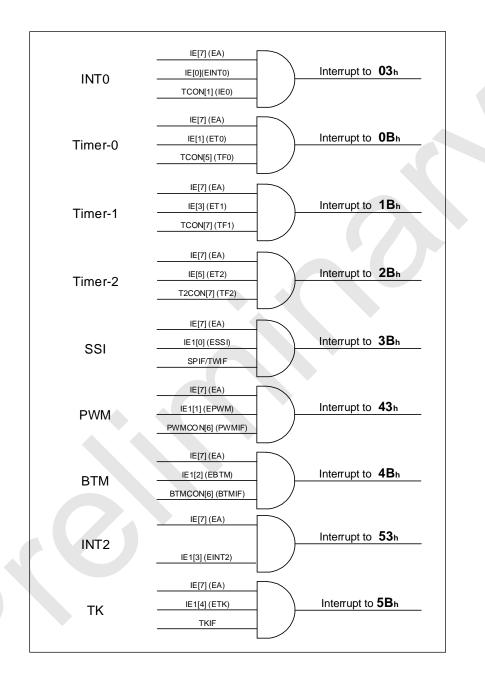

#### Interruption (INT):

- Totally 9 interrupt sources, including Timer0, Timer1, Timer2, INT0, INT2, PWM, SSI, Base Timer, TK

- Two external interrupt vectors shared by 7 external interrupt I/Os, which can be defined in

### SC92F8372/8371/8370 Super High-speed 1T 8051-based Touchkey Flash MCU

rising-edge, falling-edge or double-edge trigger mode.

• Two-level interrupt priority capability

#### **Digital Peripheral:**

- Up to 18 two-way independently controllable I/O interfaces, able to configure pull-high resistor independently

- P0, P2 4-level control drive capability

- All IOs equipped with sink current drive capability (50mA)

- 11-bit WDT, optional clock division ratio

- 3 standard 80C51 timers: Timer0, Timer1 and Timer 2

- 4 channels common cycle, duty cycle adjustable PWM

- 1 UART/SPI/IIC communication interface (SSI)

#### **Analog Peripheral:**

• 16-channel dual mode touch circuit with low power consumption can be configured for high sensitivity or high reliability mode:

- High sensitivity model to adapt to touch keys from a distance, close to the induction of sensitivity to demand higher touch application

- High reliability model has very strong anti-interference, can pass the test of 10 v dynamic CS

- Supporting 16-channels touch keys and derivative functions

- Development software library support high flexibility and low development difficult

- Automatic debugging software support, intelligent development

- When scanning with a single TouchKey in stop mode, the overall power consumption of the chip can be as low as 11uA

#### Power Saving Mode:

- IDLE Mode: can be woken up by any interrupt.

- STOP Mode: can be woken up by INT0, INT2, Base Timer and TK.

# Naming Rules for 92 Series Products

| Name | SC | 92 | F | 8 | 3 | 7 | 1 | х | М | 20 | U   |

|------|----|----|---|---|---|---|---|---|---|----|-----|

| S/R  | 1  | 2  | 3 | 4 | 5 | 6 | Ø | 8 | 9 | 10 | 11) |

| S/R  | Meaning                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------|

| 1    | SinOne Chip abbreviation                                                                                 |

| 2    | Name of product series                                                                                   |

| 3    | Product Type (F: Flash MCU)                                                                              |

| 4    | Serial Number: 7: GP Series, 8: TK series                                                                |

| 5    | ROM Size: 1 for 2K, 2 for 4K, 3 for 8K, 4 for 16K and 5 for 32K                                          |

| 6    | Subseries Number.: 0 ~ 9, A ~ Z                                                                          |

| 0    | Number of Pins: 0: 8pin, 1: 16pin, 2: 20pin, 3: 28pin, 5: 32pin, 6: 44pin, 7: 48pin, 8: 64pin, 9: 100pin |

| 8    | Version Number: (default, B, C, D)                                                                       |

| 9    | Package Type: (D: DIP; M: SOP; X: TSSOP; F: QFP; P: LQFP; Q: QFN; K: SKDIP)                              |

| 0    | Number of Pins.                                                                                          |

| (11) | Packaging Mode: (U: Tube; R: Tray; T: Reel)                                                              |

# Contents

| 1 GENERAL DESCRIPTION                                                                                                   | . 1      |

|-------------------------------------------------------------------------------------------------------------------------|----------|

| 2 FEATURES                                                                                                              | . 1      |

| NAMING RULES FOR 92 SERIES PRODUCTS                                                                                     | . 3      |

| CONTENTS                                                                                                                | . 4      |

| 3 PIN DESCRIPTION                                                                                                       | . 7      |

| 3.1 Pin Configuration                                                                                                   |          |

| 3.2 Pin Definition                                                                                                      | 8        |

| 4 INNER BLOCK DIAGRAM                                                                                                   | 11       |

| 5 FLASH ROM AND SRAM STRUCTURE                                                                                          | 12       |

| 5.1 flash rom                                                                                                           | 12       |

| 5.2 Customer Option Memory (User Programming Setting)<br>5.2.1 Customer-Option-related Registers Operation Instructions |          |

| 5.3 SRAM                                                                                                                | 17       |

| 5.3.1 Internal 256 bytes SRAM<br>5.3.2 External 128 bytes SRAM                                                          | 17<br>18 |

|                                                                                                                         | 10       |

| 6 SPECIAL FUNCTION REGISTER (SFR)                                                                                       | 19       |

| 6.1 SFR Mapping                                                                                                         | 19       |

| 6.2 SFR Instructions                                                                                                    | 20       |

| 6.2.1 C51 Core SFRs                                                                                                     | 24       |

| 7 POWER, RESET AND SYSTEM CLOCK                                                                                         | 26       |

| 7.1 Power Circuit                                                                                                       | 26       |

| 7.2 Power-on Reset                                                                                                      | 26       |

| 7.2.1 Reset Stage                                                                                                       |          |

| 7.2.2 Loading Information Stage                                                                                         |          |

| 7.2.3 Normal Operating Stage                                                                                            | 26       |

| 7.3 Reset Modes                                                                                                         | 26       |

| 7.3.1 External Reset                                                                                                    |          |

| 7.3.2 Low-voltage Reset (LVR)                                                                                           |          |

| 7.3.3 Power-on Reset (POR)                                                                                              |          |

| 7.3.4 Watchdog Reset (WDT)                                                                                              |          |

| 7.3.5 Register Reset Value                                                                                              | 30       |

| 7.4 High-speed RC Oscillator                                                                                            | 32       |

| 7.5 Low-speed RC Oscillator and Low-speed Clock Timer                                                                   | 34       |

### SC92F8372/8371/8370 Super High-speed 1T 8051-based Touchkey Flash MCU

| 7.6 STOP Mode and IDLE Mode            |       |

|----------------------------------------|-------|

| 8 CPU AND FUNCTION SYSTEM              |       |

| 8.1 CPU                                |       |

| 8.2 Addressing Mode                    | 38    |

| 8.2.1 Immediate Addressing             |       |

| 8.2.2 Direct Addressing                |       |

| 8.2.3 Indirect Addressing              |       |

|                                        |       |

| 8.2.4 Register Addressing              |       |

| 8.2.5 Relative Addressing              |       |

| 8.2.6 Indexed Addressing               |       |

| 8.2.7 Bits Addressing                  |       |

| 9 INTERRUPT                            | 40    |

| 9.1 Interrupt Source and Vector        |       |

| 9.2 Interrupt Structure Diagram        |       |

|                                        |       |

| 9.3 Interrupt Priority                 |       |

| 9.4 Interrupt Processing Flow          |       |

| 9.5 Interrupt-related Registers        |       |

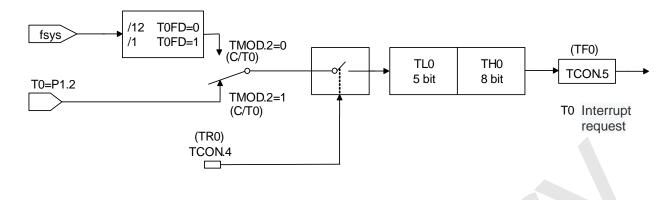

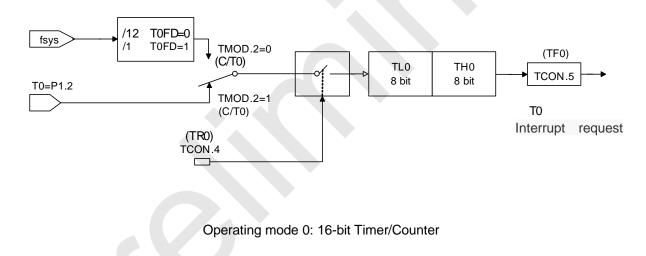

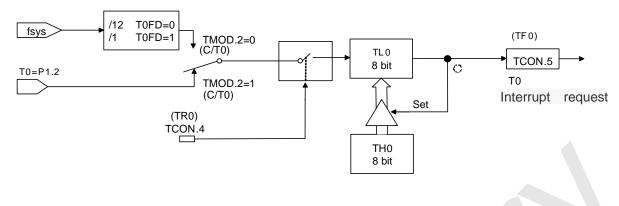

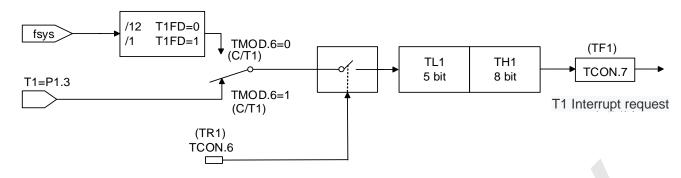

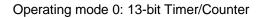

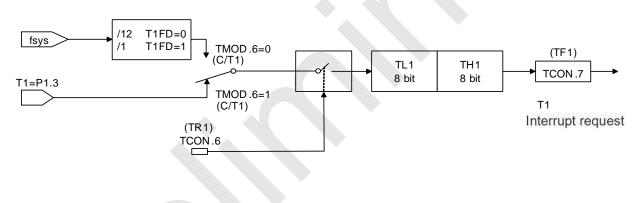

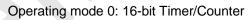

| 10 TIMER/COUNTER TO AND T1             |       |

| 10.1 T0 and T1-related Registers       |       |

| 10.2 T0 Operating Modes                |       |

| 10.3 T1 Operating Modes                |       |

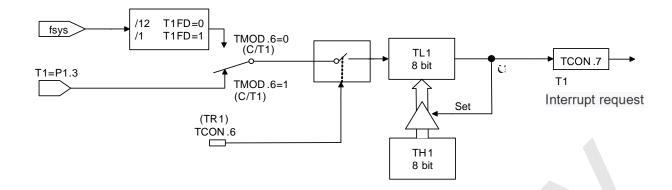

| 11 TIMER/COUNTER T2                    |       |

| 11.1 T2-related Registers              |       |

| 11.2 T2 Operating Modes                |       |

| 12 PWM                                 | 67    |

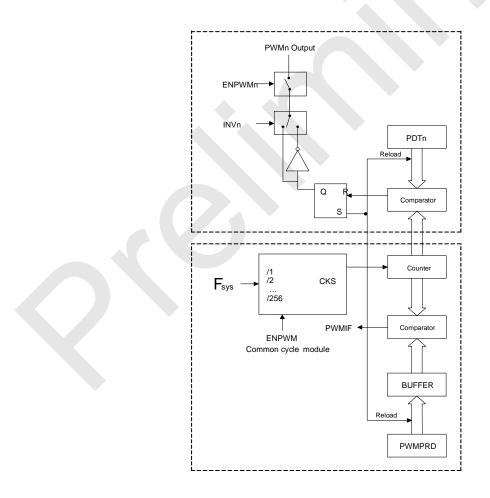

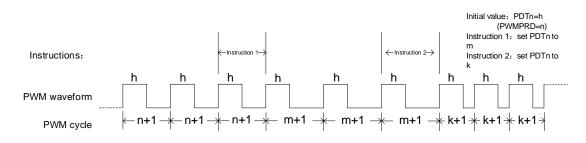

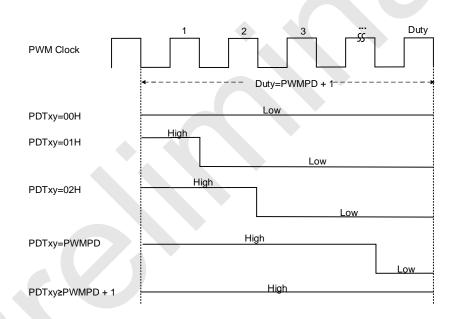

| 12.1 PWM block Diagram                 |       |

| 12.2 PWM-related Registers             |       |

| 12.3 PWM Waveforms and Directions      |       |

|                                        |       |

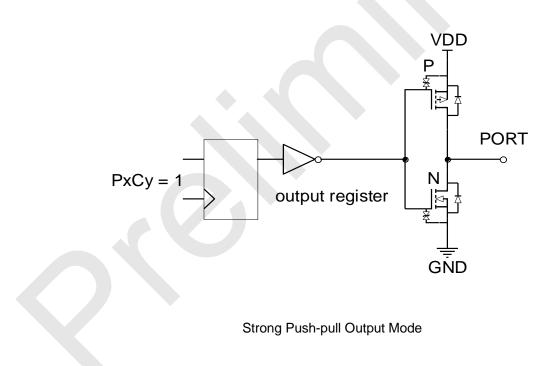

| 13 GENERAL-PURPOSE I/O (GPIO)          |       |

| 13.1 GPIO Structure Diagram            |       |

| 13.2 I/O Port-related Registers        |       |

| 14 SPI/TWI/UART SERIAL INTERFACE (SSI) | 83    |

| 14.1 Serial Peripheral Interface (SPI) |       |

| Page 5 of 123                          | \/0.1 |

# SC92F8372/8371/8370 Super High-speed 1T 8051-based Touchkey Flash MCU

| 14.1.1 SPI Operation-related Registers                     |     |

|------------------------------------------------------------|-----|

| 14.1.2 Signal Description                                  |     |

| 14.1.3 Operating Modes                                     |     |

| 14.1.4 Transfer Form                                       |     |

| 14.1.5 Error Detection                                     |     |

| 14.2 TWI                                                   |     |

|                                                            |     |

| 14.2 Two-Wire Interface (TWI)                              |     |

| 14.2.1 Signal Description                                  |     |

| 14.2.2 Operating Modes                                     |     |

| 14.2.3 Operating Steps                                     |     |

| 14.3 Serial Interface (UART)                               |     |

| 15 DOUBLE MODE TOUCH CIRCUIT                               |     |

| 15.1 The power consumption mode of the touch circuit       |     |

|                                                            |     |

| 15.2 Touch mode                                            |     |

| 16 EEPROM AND IAP OPERATIONS                               | 101 |

| 16.1 EEPROM / IAP Operating-related Registers              |     |

| 16.2 EEPROM / IAP OPerating procedures:                    |     |

| 16.2 EEPROM / IAP OPerating procedures:                    |     |

| 16.2.1 128 bytes Independent EEPROM Operating Demo program |     |

| 16.2.2 8K bytes Code memory IAP Operating Demo program     |     |

|                                                            |     |

| 17 CHECKSUM MODULE                                         |     |

| 17.1 CheckSum-Related Registers                            | 100 |

|                                                            |     |

| 18 ELECTRICAL CHARACTERISTICS                              | 111 |

|                                                            |     |

| 18.1 Absolute Maximum Ratings                              | 111 |

|                                                            |     |

| 18.2 Recommended Operating Conditions                      | 111 |

| 18.3 DC Characteristics                                    | 111 |

|                                                            |     |

| 18.4 AC Characteristics                                    | 115 |

|                                                            |     |

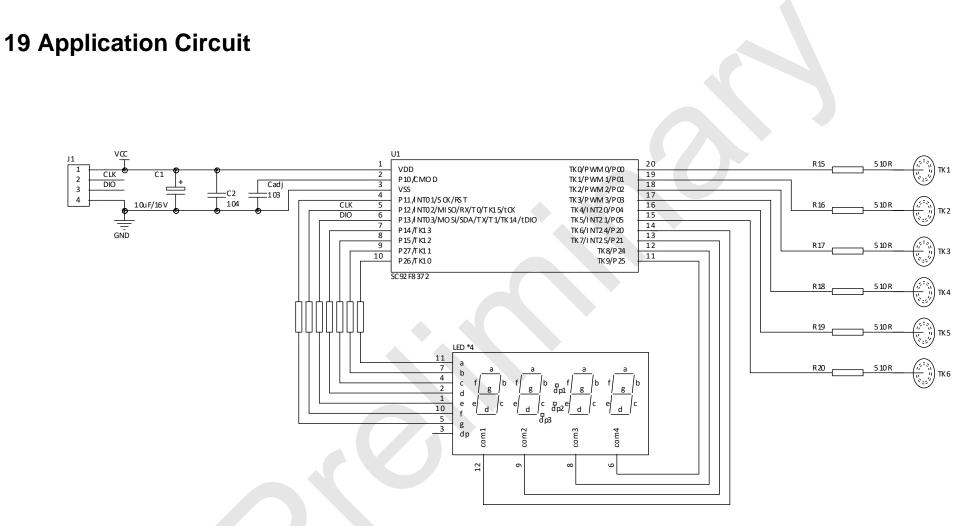

| 19 APPLICATION CIRCUIT                                     | 116 |

| 20 ORDERING INFORMATION                                    |     |

|                                                            |     |

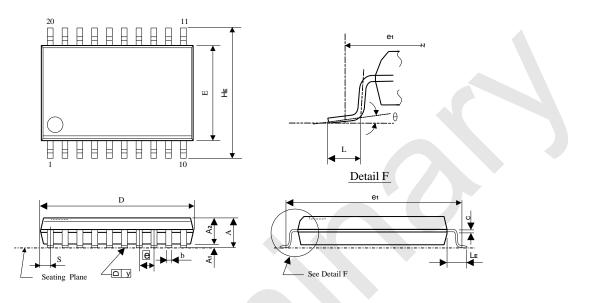

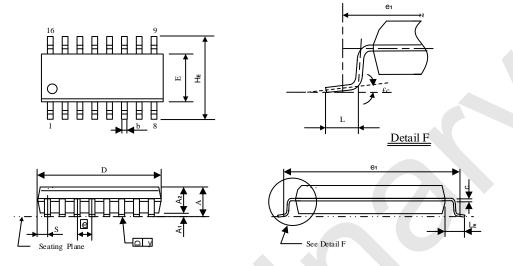

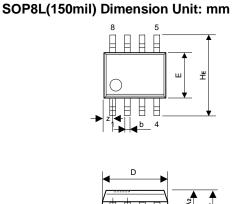

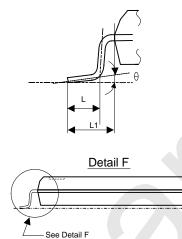

| 21 PACKAGEING INFORMATION                                  | 118 |

|                                                            |     |

| 22 REVISION HISTORY                                        | 122 |

|                                                            | 100 |

| IMPORTANT NOTICE                                           |     |

# **3 Pin Description**

### **3.1 Pin Configuration**

Note: In consideration of multiplexing of TK14/TK15 and TK debugging communication ports of the SC92F837X, if it is required to use the TK debugging function, please avoid using TK14/TK15!

The SC92F8270 Pin Diagram

### 3.2 Pin Definition

| Pin number |       | er   | Pin Name                            | Turne | Description                                                                                                               |

|------------|-------|------|-------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------|

| 20PIN      | 16pin | 8pin | rin name                            | Туре  | Description                                                                                                               |

| 1          | 1     | 1    | VDD                                 | Power | Power                                                                                                                     |

| 2          | 2     | 2    | P1.0/CMOD                           | I/O   | P1.0: GPIO P1.0<br>CMOD: Touch Key Touch<br>external capacitance                                                          |

| 3          | 3     | 3    | VSS                                 | Power | Ground                                                                                                                    |

| 4          | 4     | -    | P1.1/INT01/SCK/RST                  | 1/0   | P1.1: GPIO P1.1                                                                                                           |

|            |       |      |                                     |       | INT01: Input 1 for external interrupt 0                                                                                   |

|            |       |      |                                     |       | SCK: SPI and TWI                                                                                                          |

|            |       |      |                                     |       | RST: Reset pin                                                                                                            |

| 5          | 5     | 4    | P1.2/INT02/MISO/RX/T0/TK15/tCK      | I/O   | P1.2: GPIO P1.2                                                                                                           |

|            |       |      |                                     |       | INT02: Input 2 for external<br>interrupt 0                                                                                |

|            |       |      |                                     |       | MISO: SPI master input slave<br>output                                                                                    |

|            |       |      |                                     |       | RX: UART receive                                                                                                          |

|            |       |      |                                     |       | T0: Counter 0 external input                                                                                              |

| $\leq$     |       |      |                                     |       | TK15: TK channel 15, <b>if you</b><br>need to use TK debugging<br>function, please try to avoid<br>using this TK channel! |

|            |       |      |                                     |       | tCK: Burning and simulation                                                                                               |

| 6          | 6     | 5    | P1.3/INT03/MOSI/SDA/TX/T1/TK14/tDIO | I/O   | port clock line<br>P1.3: GPIO P1.3                                                                                        |

|            | U     | J    |                                     |       | INT03: Input 3 for external interrupt 0                                                                                   |

|            |       |      |                                     |       | MOSI: SPI main output from the input                                                                                      |

|            |       |      |                                     |       | SDA: TWI SDA                                                                                                              |

|    |    |   |                |     | TX: UART send                                                                                                      |

|----|----|---|----------------|-----|--------------------------------------------------------------------------------------------------------------------|

|    |    |   |                |     | T1: Counter 1 external input                                                                                       |

|    |    |   |                |     | TK14: TK channel 14. If you<br>need to use TK debugging<br>function, please try to avoid<br>using this TK channel! |

|    |    |   |                |     | tDIO: Data line of burning and simulation port                                                                     |

| 7  | 7  | - | P1.4/TK13      | I/O | P1.4: GPIO P1.4                                                                                                    |

|    |    |   |                |     | TK13: Channel 13 for TK                                                                                            |

| 8  | 8  | - | P1.5/TK12      | I/O | P1.5: GPIO P1.5                                                                                                    |

|    |    |   |                |     | TK12: Channel 12 for TK                                                                                            |

| 9  | -  | - | P2.7/TK11      | I/O | P2.7: GPIO P2.7<br>TK11: Channel 11 for TK                                                                         |

| 10 | 9  | - | P2.6/TK10      | I/O | P2.6: GPIO P2.6                                                                                                    |

|    |    |   |                |     | TK10: Channel 10 for TK                                                                                            |

| 11 | 10 | - | P2.5/TK9       | I/O | P2.5: GPIO P2.5                                                                                                    |

|    |    |   |                |     | TK9: Channel 9 for TK                                                                                              |

| 12 | 11 | - | P2.4/TK8       | I/O | P2.4: GPIO P2.4                                                                                                    |

|    |    |   |                |     | TK8: Channel 8 for TK                                                                                              |

| 13 | 12 | 6 | P2.1/INT25/TK7 | I/O | P2.1: GPIO P2.1                                                                                                    |

|    |    |   |                |     | INT25: Input 5 for external<br>interrupt 2                                                                         |

|    |    |   |                |     | TK7: Channel 7 for TK                                                                                              |

| 14 | 13 | 7 | P2.0/INT24/TK6 | I/O | P2.0: GPIO P2.0                                                                                                    |

|    |    |   |                |     | INT24: Input 4 for external<br>interrupt 2                                                                         |

|    |    |   |                |     | TK6: Channel 6 for TK                                                                                              |

| 15 | 14 | - | P0.5/INT21/TK5 | I/O | P0.5: GPIO P0.5                                                                                                    |

|    |    |   |                |     | INT21: Input 1 for external<br>interrupt 2                                            |

|----|----|---|----------------|-----|---------------------------------------------------------------------------------------|

|    |    |   |                |     | TK5: Channel 5 for TK                                                                 |

| 16 |    |   | P0.4/INT20/TK4 | I/O | P0.4: GPIO P0.4<br>INT20: Input 0for external<br>interrupt 2<br>TK4: Channel 4 for TK |

| 17 |    |   | P0.3/PWM3/TK3  | I/O | P0.3: GPIO P0.3<br>PWM3: PWM3 outlet<br>TK3: Channel 3 for TK                         |

| 18 |    |   | P0.2/PWM2/TK2  | I/O | P0.2: GPIO P0.2<br>PWM2: PWM2 outlet<br>TK2: Channel 2 for TK                         |

| 19 | 15 | 8 | P0.1/PWM1/TK1  | I/O | P0.1: GPIO P0.1<br>PWM1: PWM1 outlet<br>TK1: Channel 1 of TK                          |

| 20 | 16 | - | Р0.0/РШМ0/ТК0  | I/O | P0.0: GPIO P0.0<br>PWM0: PWM0 outlet<br>TK0: Channel 0 for TK                         |

# 4 Inner BLOCK Diagram

SC92F837X BLOCK DIAGRAM

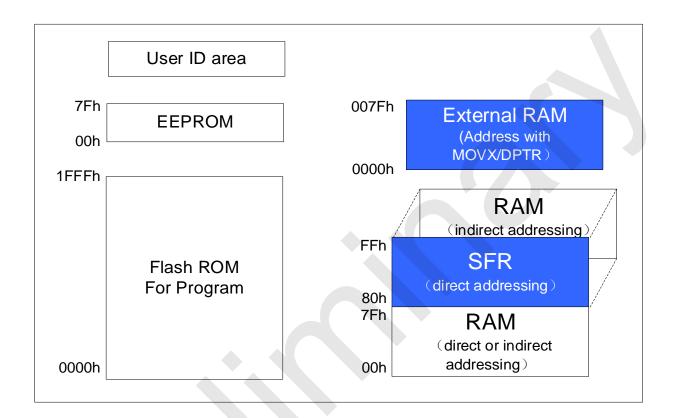

# **5 Flash ROM and SRAM Structure**

The structures of the SC92F837X's Flash ROM and SRAM are shown as follows:

#### Flash ROM and SRAM Structure Diagram

### 5.1 flash rom

The SC92F837X provides 8 Kbytes of Flash ROM with the ROM address of 0000H ~ 1FFFH. These 8 Kbytes of Flash ROM can be rewritten 10,000 times, which is able to program and erase by specialized ICP programming device (SOC PRO52/DPT52/SC LINK) provided by SinOne. The MOVC instruction is non-addressable within 256 bytes (address of 0000H ~ 00FFH).

EEPROM is a data memory separated from 8K bytes ROM with the address of 00H ~ 7FH, which can be accessed by single-byte reading and writing operations in the program; for more details, refer to <u>16 EEPROM and IAP</u> <u>Operations</u>.

# Note: The EEPROM can be rewritten 100,000 times. Users cannot exceed the limit value, otherwise there will be an exception!

The SC92F837X 8 Kbytes Flash ROM provide Empty Check, Program, Verify and Erase function other than Read function. This Flash ROM and EEPROM usually needs no Erase operation before writing. Directly writing data can realize coverage of new data.

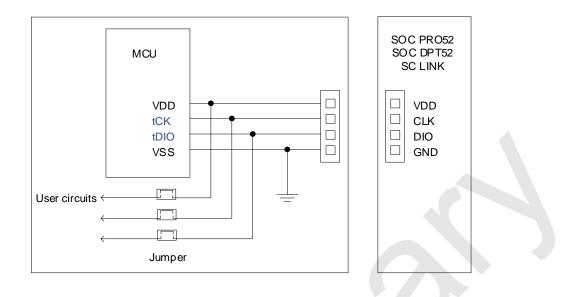

The SC92F837X Flash ROM can be programmed by tDIO, tCK, VDD and VSS, with its specific connection shown as follows:

ICP Mode Flash Writer Programming Connection Diagram

### 5.2 Customer Option Memory (User Programming Setting)

A separate Flash data memory is embedded inside the SC92F837X, called Code Option area, to save the user's presets. These presets will be written into IC when programming and loaded into SFR as default values during reset.

Option-related SFR Operating Instructions:

Reading and writing operations to option-related SFR are controlled by both register OPINX and register OPREG, with its respective address of Option SFR depending on register OPINX, as shown below:

| Symbol  | Address | Description                  | 7     | 6             | 5          | 4 | 3         | 2      | 1    | 0      |

|---------|---------|------------------------------|-------|---------------|------------|---|-----------|--------|------|--------|

| OP_HRCR | 83H@FFH | System Clock Change Register |       | OP_HRCR[7: 0] |            |   |           |        |      |        |

| OP_CTM0 | C1H@FFH | Customer Option Register 0   | ENWDT | -             | SCLKS[1:0] |   | DISRST    | DISLVR | LVRS | 6[1:0] |

| OP_CTM1 | C2H@FFH | Customer Option Register 1   | -     | -             |            |   | IAPS[1:0] |        | -    | -      |

### OP\_HRCR (83H@FFH) System Clock Change Register (Read/Write)

| Bit Number      | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------------|---|--------------|---|---|---|---|---|---|--|--|--|

| Bit<br>Mnemonic |   | OP_HRCR[7:0] |   |   |   |   |   |   |  |  |  |

| R/W             |   | R/W          |   |   |   |   |   |   |  |  |  |

| POR             | n | n            | n | n | n | n | n | n |  |  |  |

| Bit Number | Bit Mnemonic  | Description                                                                                                                                                                                |

|------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7~0        | OP_HRCR[7: 0] | Internal high-frequency RC frequency adjustment<br>Central value 10000000b corresponds to HRC central frequency, the<br>larger the value is, the faster the frequency will be, vice versa. |

### OP\_CTM0 (C1H@FFH) Customer Option Register0 (Read/Write)

| Bit Number      | 7     | 6 | 5    | 4       | 3      | 2      | 1          | 0 |

|-----------------|-------|---|------|---------|--------|--------|------------|---|

| Bit<br>Mnemonic | ENWDT |   | SCLK | S[1: 0] | DISRST | DISLVR | LVRS[1: 0] |   |

| R/W             | R/W   | - | R/   | W       | R/W    | R/W    | R/         | W |

| POR             | n     | x | n    |         | n      | n      | r          | 1 |

| Bit Number | Bit Mnemonic | Description                                                                                                                   |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------|

| 7          | ENWDT        | Watchdog (WDT) control bit (This bit is transferred by the system to the value set by the user Code Option)<br>0: WDT invalid |

### Super High-speed 1T 8051-based Touchkey Flash MCU

|       |             | 1: WDT valid (WDT stops counting during IAP execution)     |

|-------|-------------|------------------------------------------------------------|

| 5 ~ 4 | SCLKS[1: 0] | System clock frequency selection bits                      |

|       |             | 00: Reserved;                                              |

|       |             | 01: System clock frequency is HRC frequency divided by 2;  |

|       |             | 10: System clock frequency is HRC frequency divided by 4;  |

|       |             | 11: System clock frequency is HRC frequency divided by 12; |

| 3     | DISRST      | IO/RST selection bit                                       |

|       |             | 0: configure P1.1 as External Reset input pin              |

|       |             | 1: configure P1.1 as GPIO                                  |

| 2     | DISLVR      | LVR control bit                                            |

|       |             | 0: LVR valid                                               |

|       |             | 1: LVR invalid                                             |

| 1 ~ 0 | LVRS [1: 0] | LVR voltage selection bits                                 |

|       | •           | 11: 4.3V reset                                             |

|       |             | 10: 3.7 V reset                                            |

|       |             | 01: 2.9V reset                                             |

|       |             | 00: 2.3 V reset                                            |

| 6     |             | Reserved                                                   |

### OP\_CTM1 (C2H@FFH) Customer Option Register1 (Read/Write)

| Bit Number      | 7 | 6 | 5 | 4 | 3 2       |  | 1 | 0 |

|-----------------|---|---|---|---|-----------|--|---|---|

| Bit<br>Mnemonic | - | - | - | - | IAPS[1:0] |  | - | - |

| R/W             | - | - | - | - | R/W R/W   |  | - | - |

| POR             | x | x | х | х | n n       |  | x | x |

| Bit Number | Bit Mnemonic | Description                                                                                                                                 |

|------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 3~2        | IAPS[1: 0]   | EEPROM and IAP Area Selection Bits                                                                                                          |

|            |              | 00: Code memory prohibits IAP operations                                                                                                    |

|            |              | 01: last 0.5k code memory allows IAP operation                                                                                              |

|            |              | <ul><li>10: Last 1k code memory allows IAP operation (0C00H~0FFFH)</li><li>11: All code memory allows IAP operation (0000H~0FFFH)</li></ul> |

| 7~4,1~0    | -            | Reserved                                                                                                                                    |

### 5.2.1 Customer-Option-related Registers Operation Instructions

Option-related SFRs reading and writing operations are controlled by both OPINX and OPREG registers, with their respective position of Option SFR depending on OPINX and its value written to option-related SFR depending on register OPREG:

| Symbol | Address | Description     |             | POR      |

|--------|---------|-----------------|-------------|----------|

| OPINX  | FEH     | Option Pointer  | OPINX[7: 0] | 0000000b |

| OPREG  | FFH     | Option Register | OPREG[7: 0] | nnnnnnb  |

When operating Option-related SFRs, register OPINX stores the address of option-related registers and register OPREG stores corresponding value.

For Example: To configure OP\_HRCR as 0x01, specific operation method is shown below:

C program example:

| OPINX = 0x83; | //Write OP_HRCR address into OPINX register                                      |

|---------------|----------------------------------------------------------------------------------|

| OPREG = 0x01; | //Write 0x01 into OPREG register (the value to be written into OP_HRCR register) |

Assembler program example:

| MOV OPINX, #83H;                      | //Write OP_HRCR address into OPINX register                    |  |  |  |  |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|--|--|

| MOV OPREG, #01H;<br>OP_HRCR register) | //Write 0x01 into OPREG register (the value to be written into |  |  |  |  |  |  |  |  |

Note: It is forbidden to write any value beyond SFR address of Customer Option region into OPINX register! Or else, it may cause abnormal system operation.

### 5.3 SRAM

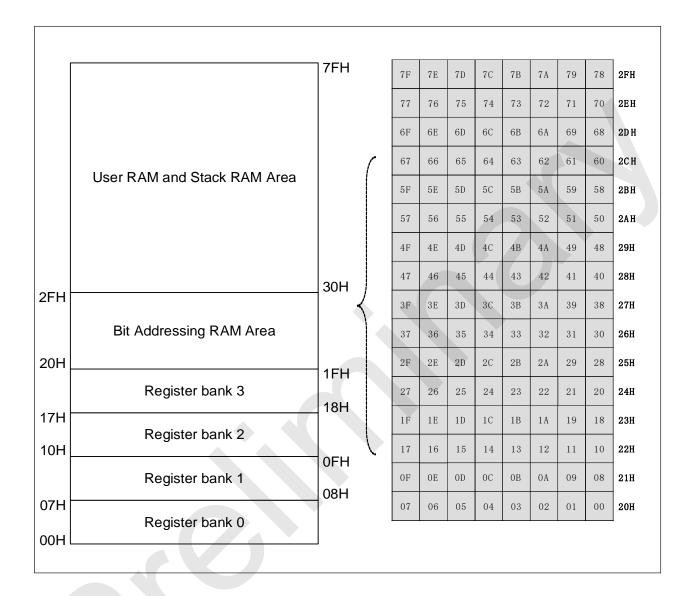

SC92F837X MCU integrates SRAM with 384 Bytes, which is divided into internal 256 Bytes RAM and external 128 Bytes RAM. The internal RAM ranges from 00H to FFH, with high 128 Bytes (address 80H~FFH) addressing only indirectly and low 128 Bytes (address 00H~7FH) addressing either directly or indirectly.

The address of the special function register SFR is also 80H~FFH. The difference between the SFR and the internal high 128 Bytes SRAM is that the SFR register is directly addressed, while the internal high 128 Bytes SRAM can only be indirectly addressed.

The external RAM address is 0000H~07FH, but it needs to be addressed via the MOVX directive.

### 5.3.1 Internal 256 bytes SRAM

Internal low 128 bytes SRAM area is divided into three parts:

- 1. Register bank 0 ~ 3, address from 00H to 1FH. The RS1 and RS0 of PSW register can select the currently active SFR. Using Register bank 0 ~ 3 can accelerate arithmetic speed;

- Bit addressing area, 20H ~2FH; user can use it as normal RAM or bitwise addressing RAM; for the latter, the bit address is from 00H to 7FH (bitwise addressing is different from normal SRAM byte-oriented addressing), which can be distinguished by instructions in program;

- 3. User RAM and stack area, the 8-bit stack pointer will point to stack area after the SC92F837X reset; in general, users can set initial value in initializer, it is recommended to configure in the unit interval from E0H to FFH.

|                                                                      | ך FFH            |                                        | FFH |

|----------------------------------------------------------------------|------------------|----------------------------------------|-----|

| High 128 bytes RAM<br>Accessible by indirect addressing only         | 80H              | SFR<br>Accessible by direct addressing | 80H |

|                                                                      | ] 7FH            |                                        |     |

|                                                                      |                  |                                        |     |

| Low 128 bytes RAM<br>Accessible by direct and indirect<br>addressing |                  |                                        |     |

|                                                                      | _ <sub>00Н</sub> |                                        |     |

### SC92F8372/8371/8370 Super High-speed 1T 8051-based Touchkey Flash MCU

#### Internal 256 bytes RAM Structure Diagram

Internal low 128 bytes RAM structure is shown below:

SRAM Structure Diagram

### 5.3.2 External 128 bytes SRAM

External 128 Bytes SRAM supports traditional access to external RAM methods. Use MOVX A, @Ri or MOVX @Ri, A to access external 128 Bytes RAM; External 128 Bytes RAM can also be accessed using MOVX A, @DPTR or MOVX @DPTR, A.

# 6 Special Function Register (SFR)

### 6.1 SFR Mapping

The SC92F837X provides some registers equipped with special functions, called SFR. The address of such SFRs is from 80H to FFH, some are bit-addressable, and others are not. It is very convenient for these bit addressable registers to change the value of single bit, of which the address is end up with figure "0" or "8". All SFR shall use direct addressing for addressing.

The name and address of the SC92F837X special function registers are shown in the table below:

|     | 0/8   | 1/9    | 2/A      | 3/B        | 4/C     | 5/D     | 6/E     | 7/F     |

|-----|-------|--------|----------|------------|---------|---------|---------|---------|

| F8h | -     | -      | -        | -          | CHKSUML | СНКЅՍМН | OPINX   | OPREG   |

| F0h | В     | IAPKEY | IAPADL   | IAPADH     | IAPADE  | IAPDAT  | IAPCTL  | -       |

| E8h | -     | -      | -        | -          | -       | -       | -       | OPERCON |

| E0h | ACC   | -      | -        |            |         | -       | -       | -       |

| D8h | -     | -      | -        |            | _       | -       | -       | -       |

| D0h | PSW   | PWMCFG | PWMCON   | PWMPRD     | PWMDTY3 | PWMDTY0 | PWMDTY1 | PWMDTY2 |

| C8h | T2CON |        | RCAP2L   | RCAP2H TL2 |         | TH2     | BTMCON  | WDTCON  |

| C0h | -     |        | <u> </u> | -          |         |         | INT2F   | INT2R   |

| B8h | IP    | IP1    | INTOF    | INTOR      |         |         |         |         |

| B0h | -     |        | -        | -          | -       | -       | -       | -       |

| A8h | IE    | IE1    |          |            | -       | -       |         |         |

| A0h | P2    | P2CON  | P2PH     | -          | -       | -       | -       | -       |

| 98h | -     | -      | P0CON    | P0PH       | -       | SSCON0  | SSCON1  | SSDAT   |

| 90h | P1    | P1CON  | P1PH     | -          | -       | SSCON2  | -       | IOHCON  |

| 88h | TCON  | TMOD   | TLO      | TL1        | TH0     | TH1     | TMCON   | OTCON   |

Super High-speed 1T 8051-based Touchkey Flash MCU

| 80h | P0              | SP DPL DPH      |  |  |                  | -   | PCON |  |

|-----|-----------------|-----------------|--|--|------------------|-----|------|--|

|     | Bit Addressable | Bit Addressable |  |  | Not Bit Addressa | ble |      |  |

Notes:

- 1. The hollow spaces in the table above means that there is no such register RAM, which is not recommended for users.

- 2. The address of SFR for system configuration is F1H ~ FFH, user use it may result in system exceptions. Users are not allowed to conduct clearing or other operations to these registers during the system initialization process.

### 6.2 SFR Instructions

For details on each SFR, see the following table:

| Mnemonic | Add | Description                          | 7    | 6        | 5   | 4   | 3      | 2    | 1    | 0         | POR       |

|----------|-----|--------------------------------------|------|----------|-----|-----|--------|------|------|-----------|-----------|

| P0       | 80H | P0 Data Register                     | -    | -        | P05 | P04 | P03    | P02  | P01  | P00       | xx000000b |

| SP       | 81H | Stack Pointer                        |      |          |     | SP[ | 7:0]   |      |      |           | 00000111b |

| DPL      | 82H | Data Pointer Low byte                |      |          |     | DPL | [7:0]  |      |      |           | 00000000b |

| DPH      | 83H | Data Pointer High byte               |      |          |     | DPH | I[7:0] |      |      |           | 0000000b  |

| PCON     | 87H | Power Management Control<br>Register | SMOD | _        | -   | -   | -      | -    | STOP | IDL       | 0xxxxx00b |

| TCON     | 88H | Timer Control Register               | TF1  | TR1      | TF0 | TR0 | -      | -    | IE0  | -         | 0000xx0xb |

| TMOD     | 89H | Timer Operating Mode<br>Register     | -    | C/T1     | M11 | M01 | -      | C/T0 | M10  | M00       | x000x000b |

| TLO      | 8AH | Timer0 Low 8 bits                    |      |          |     | TLO | [7:0]  |      |      |           | 00000000Ь |

| TL1      | 8BH | Timer1 Low 8 bits                    |      | TL1[7:0] |     |     |        |      |      | 00000000b |           |

| тно      | 8CH | Timer0 High 8 bits                   |      | TH0[7:0] |     |     |        |      |      | 0000000b  |           |

| TH1      | 8DH | Timer1 High 8 bits                   |      |          |     | TH1 | [7:0]  |      |      |           | 00000000b |

| TMCON  | 8EH | Timer Frequency Control<br>Register            | -        | -      | -    | -     | -       | T2FD   | T1FD | TOFD  | xxxxx000b |

|--------|-----|------------------------------------------------|----------|--------|------|-------|---------|--------|------|-------|-----------|

| OTCON  | 8FH | Output Control Register                        | SSMC     | D[1:0] | -    | -     | -       | -      | -    | -     | 00xxxxxb  |

| P1     | 90H | P1 data register                               | -        | -      | P15  | P14   | P13     | P12    | P11  | P10   | xx000000b |

| P1CON  | 91H | P1 Input/output control register               | -        | -      | P1C5 | P1C4  | P1C3    | P1C2   | P1C1 | P1C0  | xx000000b |

| P1PH   | 92H | P1 pull up resistance<br>control register      | -        | -      | P1H5 | P1H4  | P1H3    | P1H2   | P1H1 | P1H0  | xx000000b |

| SSCON2 | 95H | SSI control register 2                         |          |        |      | SSCO  | N2[7:0] |        |      |       | 0000000b  |

| IOHCON | 97H | IOH sets registers                             | P2H      | [1:0]  | P2L  | [1:0] | POH     | I[1:0] | POL  | [1:0] | 00000000b |

| POCON  | 9AH | P0 input/output control register               | -        | -      | P0C5 | P0C4  | P0C3    | P0C2   | P0C1 | P0C0  | xx000000b |

| РОРН   | 9BH | Port P0 pull-up resistance<br>control register | <u> </u> |        | P0H5 | P0H4  | P0H3    | P0H2   | P0H1 | P0H0  | xx000000b |

| SSCON0 | 9DH | SSI control register 0                         |          |        |      | SSCO  | N0[7:0] |        |      |       | 0000000b  |

| SSCON1 | 9EH | SSI control register 1                         |          |        |      | SSCO  | N1[7:0] |        |      |       | 00000000b |

| SSDAT  | 9FH | SSI data register                              |          |        |      | SSD   | [7:0]   |        |      |       | 00000000b |

| P2     | АОН | P2 port data register                          | P27      | P26    | P25  | P24   | -       | -      | P21  | P20   | 0000x00b  |

| P2CON  | A1H | P2 port Input/output control register          | P2C7     | P2C6   | P2C5 | P2C4  | -       | -      | P2C1 | P2C0  | 0000x00b  |

| P2PH   | A2H | P2 port pull up resistance<br>control register | P2H7     | P2H6   | P2H5 | P2H4  | -       | -      | P2H1 | P2H0  | 0000x00b  |

| IE     | A8H | Interrupt enable register                      | EA       | -      | ET2  | -     | ET1     | -      | ET0  | EINT0 | 0x0x0x00b |

| IE1    | A9H | Interrupt enable register 1                    | -        | -      | -    | ЕТК   | EINT2   | EBTM   | EPWM | ESSI  | xxx00000b |

| IP     | B8H | Interrupt priority control register               | -                    | -                       | IPT2   | -      | IPT1    | -      | IPT0      | IPINT0 | xx0x0x00b |  |

|--------|-----|---------------------------------------------------|----------------------|-------------------------|--------|--------|---------|--------|-----------|--------|-----------|--|

| IP1    | B9H | Interrupt priority control register 1             | -                    | -                       | -      | IPTK   | IPINT2  | IPBTM  | IPPWM     | IPSSI  | xxx00000b |  |

| INTOF  | BAH | INT0 drop edge interrupt<br>control register      | _                    | _                       | -      | -      | INT0F3  | INT0F2 | INT0F1    | -      | xxxx000xb |  |

| INTOR  | BBH | INT0 upedge interrupt<br>control register         | _                    | _                       | -      | -      | INT0R3  | INT0R2 | INT0R1    |        | xxxx000xb |  |

| INT2F  | С6Н | INT2 drop edge interrupt<br>control register      | _                    | _                       | INT2F5 | INT2F4 | -       | Ċ      | INT2F1    | INT2F0 | xx00xx00b |  |

| INT2R  | С7Н | INT2 ascending edge<br>interrupt control register | _                    | _                       | INT2R5 | INT2R4 |         |        | INT2R1    | INT2R0 | xx00xx00b |  |

| T2CON  | C8H | Timer 2 controls registers                        | TF2                  | -                       |        | •      |         | TR2    | -         | -      | 0xxxx0xxb |  |

| RCAP2L | CAH | Timer 2 overload 8 bits low                       |                      | RCAP2L[7:0]             |        |        |         |        |           |        |           |  |

| RCAP2H | СВН | Timer 2 overload 8 bits high                      |                      |                         |        | RCAP   | 2H[7:0] |        |           |        | 0000000b  |  |

| TL2    | ссн | Timer 2 is 8 bits low                             |                      |                         |        | TL2    | [7:0]   |        |           |        | 0000000b  |  |

| TH2    | CDH | Timer 2 is 8 bits high                            |                      |                         |        | TH2    | [7:0]   |        |           |        | 0000000b  |  |

| BTMCON | СЕН | Low frequency timer control register              | ENBTM                | BTMIF                   | -      | -      |         | BTMF   | S[3:0]    |        | 00xx0000b |  |

| WDTCON | CFH | WDT control register                              | CLRWDT - WDTCKS[2:0] |                         |        |        |         |        | xxx0x000b |        |           |  |

| PSW    | D0H | Program state word register                       | CY                   | AC                      | F0     | RS1    | RS0     | ov     | F1        | Р      | 0000000b  |  |

| PWMCFG | D1H | PWM setting register                              | F                    | PWMCKS[2:0] - INV3 INV2 |        |        |         |        | INV1      | INV0   | 000x0000b |  |

| PWMCON | D2H | PWM control register                              | ENPWM                | PWMIF                   | -      | -      | ENPWM3  | ENPWM2 | ENPWM1    | ENPWM0 | 00xx0000b |  |

| PWMPRD | D3H | PWM cycle setting register                        |                      | PWMPRD[7:0]             |        |        |         |        |           |        |           |  |

| PWMDTY3 | D4H | PWM3 duty ratio setting                     |   | PDT3[7:0]    |   |        |               |           |           |  |  |

|---------|-----|---------------------------------------------|---|--------------|---|--------|---------------|-----------|-----------|--|--|

|         |     | register                                    |   |              |   |        |               |           |           |  |  |

| PWMDTY0 | D5H | PWM0 duty ratio setting<br>register         |   | PDT0[7:0]    |   |        |               |           |           |  |  |

| PWMDTY1 | D6H | PWM1 duty ratio setting<br>register         |   | PDT1[7:0]    |   |        |               |           |           |  |  |

| PWMDTY2 | D7H | PWM2 duty ratio setting<br>register         |   |              |   | PDT2   | [7:0]         |           | 00000006  |  |  |

| ACC     | E0H | accumulator                                 |   |              |   | ACC    | [7:0]         |           | 00000000ь |  |  |

| OPERCON | EFH | Operation control register                  | - | -            | - | -      |               | - CHKSUMS | xxxxxx0b  |  |  |

| В       | F0H | Register B                                  |   |              |   | B[7    | :0]           |           | 0000000ь  |  |  |

| IAPKEY  | F1H | IAP protects registers                      |   | IAPKEY[7:0]  |   |        |               |           |           |  |  |

| IAPADL  | F2H | IAP writes to the low 8-bit register        |   |              |   | IAPAD  | R[7:0]        |           | 00000000Ь |  |  |

| IAPADH  | F3H | IAP writes to the high 5-bit register       |   |              |   |        | IAPADR[12:8   | 3]        | xxx00000b |  |  |

| IAPADE  | F4H | IAP writes to the extended address register |   |              |   | IAPADE | ER[7:0]       |           | 0000000ь  |  |  |

| IAPDAT  | F5H | IAP data register                           |   |              |   | IAPDA  | T[7:0]        |           | 0000000b  |  |  |

| IAPCTL  | F6H | IAP control register                        | - | -            | - | -      | PAYTIMES[1:0] | CMD[1:0]  | xxxx0000b |  |  |

| CHKSUML | FCH | Check Sum results register<br>low           |   | CHKSUML[7:0] |   |        |               |           |           |  |  |

| CHKSUMH | FDH | Check Sum result register<br>high           |   | CHKSUMH[7:0] |   |        |               |           |           |  |  |

| OPINX   | FEH | Option a pointer                            |   |              |   | OPIN   | K[7:0]        |           | 0000000b  |  |  |

| OPREG   | FFH | The Option register                         |   |              |   | OPRE   | G[7:0]        |           | nnnnnnb   |  |  |

### 6.2.1 C51 Core SFRs

### Program Counter (PC)

PC does not belong to SFR .16-bit PC is the register used to control instruction execution sequence. After poweron or reset of micro controller unit, PC value is 0000H, that is to say, the micro controller unit is to execute program from 0000H.

#### Accumulator ACC (E0H)

Accumulator ACC is one of the commonly-used registers in 8051-based micro controller unit, using A as mnemonic symbol in the instruction system. It is usually used to store operand and results for calculation or logical operations.

#### B Register (F0H)

B Register shall be used together with Accumulator A in multiplication and division operations. For example, instruction "MUL A, B" is used to multiply 8-bit unsigned numbers of Accumulator A and Register B. As for the acquired 16-bit product, low byte is placed in A and High byte in B. As for "DIV A, B" is used to divide A by B, place integer quotient in A and remainder in B. Register B can also be used as common temporary register.

#### Stack Pointer SP (81H)

Stack pointer is an 8-bit specialized register, it indicates the address of top stack in common RAM. After resetting of micro controller unit, the initial value of SP is 07H, and the stack will increase from 08H. 08H ~ 1FH is address of register banks 1 ~ 3.

#### PSW (D0H) Program Status Word Register (Read/Write)

| Bit Number      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit<br>Mnemonic | СҮ  | AC  | F0  | RS1 | RS0 | OV  | F1  | Ρ   |

| R/W             | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR             | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit Number | Bit Mnemonic | Description |

|------------|--------------|-------------|

|------------|--------------|-------------|

| 7     | СҮ      | Carry Flag bit                                                                                                   |                            |                                                              |  |  |  |  |

|-------|---------|------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------|--|--|--|--|

|       |         | 1: The top digit of add operation has carry bit or the top digit of subtraction operation has the borrow digit   |                            |                                                              |  |  |  |  |

|       |         | 0: The top digit of add operation has no carry bit or the top digit of subtraction operation has no borrow digit |                            |                                                              |  |  |  |  |

| 6     | AC      |                                                                                                                  | auxiliary<br>n operatic    | flag bit (adjustable upon BCD code add and ons)              |  |  |  |  |

|       |         |                                                                                                                  | s carry bit<br>traction op | in bit 3 upon add operation and borrow bit in bit 3 peration |  |  |  |  |

|       |         | 0: No bor                                                                                                        | row bit and                | d carry bit                                                  |  |  |  |  |

| 5     | F0      | User flag                                                                                                        | bit                        |                                                              |  |  |  |  |

| 4 ~ 3 | RS1、RS0 | Register b                                                                                                       | oanks sele                 | ection bits                                                  |  |  |  |  |

|       |         | RS1                                                                                                              | RS0                        | Current Selected Register banks 0 ~ 3                        |  |  |  |  |

|       |         | 0                                                                                                                | 0                          | Group 0 (00H ~ 07H)                                          |  |  |  |  |

|       |         | 0                                                                                                                | 1                          | Group 1 (08H ~ 0FH)                                          |  |  |  |  |

|       |         | 1                                                                                                                | 0                          | Group 2 (10H ~ 17H)                                          |  |  |  |  |

|       |         | 1                                                                                                                | 1                          | Group 3 (18H ~ 1FH)                                          |  |  |  |  |

| 2     | ον      | Overflow                                                                                                         | flag bit                   |                                                              |  |  |  |  |

| 1     | F1      | F1 flag bit                                                                                                      | t                          |                                                              |  |  |  |  |

|       |         | User cust                                                                                                        | omized fla                 | ng                                                           |  |  |  |  |

| 0     | Ρ       | Parity flag<br>accumula                                                                                          |                            | flag bit is the parity value of the number of 1 in           |  |  |  |  |

|       |         | 1: Odd nu                                                                                                        | Imber of n                 | umber of 1 in ACC                                            |  |  |  |  |

|       |         | 0: Even n                                                                                                        | umber of I                 | number of 1 in ACC (including 0)                             |  |  |  |  |

### Data Pointer DPTR (82H, 83H)

The data pointer DPTR is a 16-bit special register consisting of a low 8-bit DPL (82H) and a high 8-bit DPH (83H). DPTR is the only register in the traditional 8051 kernel micro controller that can directly carry out 16-bit operation, and can also carry out operation on DPL and DPH by byte respectively.

# 7 Power, Reset and System Clock

### 7.1 Power Circuit

The SC92F837X Power includes circuits such as BG, LDO, POR and LVR, which are able to reliably work within the scope of  $2.4V \sim 5.5V$ .

### 7.2 Power-on Reset

After the SC92F837X power-on, the processes carried out before execution of client software are as follows:

- Reset stage

- Loading information stage

- Normal operation stage

### 7.2.1 Reset Stage

The SC92F837X will always be in reset mode. There will not be a valid clock until the voltage supplied to the SC92F837X is higher than certain voltage. The duration of reset stage is related to rising speed of external power. Once the external supply voltage is up to built-in POR voltage, the reset stage would be completed.

### 7.2.2 Loading Information Stage

There is a preheating counter inside the SC92F837X. During the reset stage, this preheating counter is always reset as zero. After the voltage is higher than POR voltage, internal RC oscillator starts to oscillate and this preheating counter starts to count. When internal preheating counter counts up to certain number, one byte data will be read from IFB of Flash ROM (including Code Option) for every certain number of HRC clock, which is saved to internal system registers. After the preheating is completed, such reset signal will end.

### 7.2.3 Normal Operating Stage

After the loading information stage has been completed, the SC92F837X starts to read instruction code from Flash and enters normal operating stage. At this time, LVR voltage is the set value of Code Option written by user.

### 7.3 Reset Modes

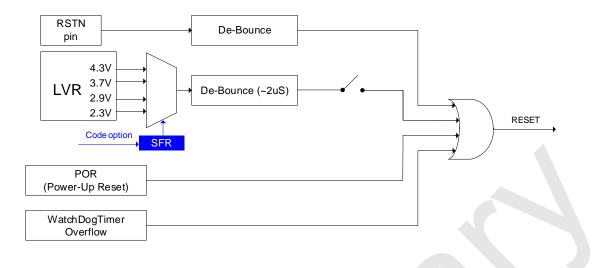

The SC92F837X has 4 kinds of reset modes: ① External RST reset ②Low-voltage reset (LVR) ③Power-on reset (POR) ④Watchdog (WDT) reset.

### 7.3.1 External Reset

Page 26 of 123

External reset is to supply a certain width reset pulse signal to the SC92F837X from the RST pin to realize the SC92F837X reset.

RST/SCK/INT01/P1.1 has a reset function. Before burning the program, users can modify it to a non-reset pin by burning the host computer software to configure the Customer Option.

### 7.3.2 Low-voltage Reset (LVR)

The SC92F837X provides a low-voltage reset circuit. There are 4-level LVR voltage options: 4.3V, 3.7V, 2.9V and 2.3V. The default is the Option value written by user.

#### OP\_CTM0(C1H@FFH) Customer Option Register 0 (Read/Write)

| Bit Number      | 7     | 6 | 5           | 4 | 3      | 2      | 1          | 0 |

|-----------------|-------|---|-------------|---|--------|--------|------------|---|

| Bit<br>Mnemonic | ENWDT | - | SCLKS[1: 0] |   | DISRST | DISLVR | LVRS[1: 0] |   |

| R/W             | R/W   | - | R/W         | • | Ŕ/W    | R/W    | R/W        |   |

| POR             | n     | x | n           |   | n      | n      | n          |   |

| Bit Number | Bit Mnemonic | Description                                                                                            |

|------------|--------------|--------------------------------------------------------------------------------------------------------|

| 2          | DISLVR       | LVR control bit<br>0: LVR valid<br>1: LVR invalid                                                      |

| 1~0        | LVRS [1: 0]  | LVR voltage selection bits<br>11: 4.3 V reset<br>10: 3.7 V reset<br>01: 2.9 V reset<br>00: 2.3 V reset |

The Circuit Diagram of the SC92F837X Resetting Part is shown below:

#### The SC92F837X Reset Diagram

### 7.3.3 Power-on Reset (POR)

The SC92F837X provides a power-on reset circuit. When power voltage  $V_{DD}$  is up to POR reset voltage, the system will be reset automatically.

### 7.3.4 Watchdog Reset (WDT)

The SC92F837X has a WDT, the clock source of which is the internal 128 kHz oscillator. User can select whether to enable Watchdog Reset function by programmer Code Option.

| Bit Number      | 7     | 6 | 5 4         | 3      | 2      | 1          | 0 |

|-----------------|-------|---|-------------|--------|--------|------------|---|

| Bit<br>Mnemonic | ENWDT |   | SCLKS[1: 0] | DISRST | DISLVR | LVRS[1: 0] |   |

| R/W             | R/W   | - | R/W         | R/W    | R/W    | R/W        |   |

| POR             | n     | x | n           | n      | n      | n          |   |

OP\_CTM0 (C1H@FFH) Customer Option Register 0 (Read/Write)

| Bit Number | Bit Mnemonic | Description                                                                                                         |

|------------|--------------|---------------------------------------------------------------------------------------------------------------------|

| 7          | ENWDT        | WDT control bit (This bit is transferred by the system to the value set<br>by the user Code Option)<br>1: WDT valid |

Super High-speed 1T 8051-based Touchkey Flash MCU

|  | 0: WDT invalid |

|--|----------------|

|--|----------------|

### WDTCON (CFH) WDT Control Register (Read/Write)

| Bit Number      | 7 | 6 | 5 | 4      | 3 | 2            | 1 | 0 |  |

|-----------------|---|---|---|--------|---|--------------|---|---|--|

| Bit<br>Mnemonic | - | - | - | CLRWDT | - | WDTCKS[2: 0] |   |   |  |

| R/W             | - | - | - | R/W    | - | R/W          |   |   |  |

| POR             | x | x | x | 0      | x | 0            | 0 | 0 |  |

|                 |   |   |   |        |   |              |   |   |  |

| Bit Number | Bit Mnemonic  | Description                                                                                |                   |  |  |  |  |

|------------|---------------|--------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| 4          | CLRWDT        | Clear WDT (Only valid when set to 1)<br>1: WDT counter restart, cleared by system hardware |                   |  |  |  |  |

| 2~0        | WDTCKS [2: 0] | WDT clock selection bits                                                                   |                   |  |  |  |  |

|            |               | WDTCKS[2: 0]                                                                               | WDT overflow time |  |  |  |  |

|            |               | 000                                                                                        | 500ms             |  |  |  |  |

|            |               | 001                                                                                        | 250ms             |  |  |  |  |

|            |               | 010                                                                                        | 125ms             |  |  |  |  |

|            |               | 011                                                                                        | 62.5ms            |  |  |  |  |

|            |               | 100                                                                                        | 31.5ms            |  |  |  |  |

|            |               | 101                                                                                        | 15.75ms           |  |  |  |  |

|            |               | 110                                                                                        | 7.88ms            |  |  |  |  |

Super High-speed 1T 8051-based Touchkey Flash MCU

|          |   | 111      | 3.94ms |  |

|----------|---|----------|--------|--|

| 7 ~ 5, 3 | - | Reserved |        |  |

### 7.3.5 Register Reset Value

During reset, most registers are set to their initial values and the WDT remains disable. The PORT register is FFh. The initial value of program counter (PC) is 0000h, and the initial value of stack pointer SP is 07h. Reset of "Hot Start" (such as WDT, LVR, etc.) will not influence SRAM which always keep the value before resetting. The SRAM contents will be retained until the power voltage is too low to keep RAM alive.

The initial value of power-on reset in SFRs is shown in the table below:

| Mnemonic | Reset value | Mnemonic | Reset value |

|----------|-------------|----------|-------------|

| ACC      | 0000000b    | P1PH     | xx000000b   |

| В        | 0000000b    | P2       | 0000xx00b   |

| PSW      | 0000000b    | P2CON    | 0000xx00b   |

| SP       | 00000111b   | P2PH     | 0000xx00b   |

| DPL      | 0000000b    | PWMCFG   | 00x00000b   |

| DPH      | 0000000b    | PWMCON   | 00xx0000b   |

| PCON     | 0xxxxx00b   | PWMDTY3  | 0000000b    |

| BTMCON   | 00xx0000b   | PWMDTY0  | 0000000b    |

| IAPADE   | 0000000b    | PWMDTY1  | 0000000b    |

| IAPADH   | xxx00000b   | PWMDTY2  | 0000000b    |

| IAPADL   | 0000000b    | PWMPRD   | 0000000b    |

| IAPCTL   | xxxx0000b   | RCAP2H   | 0000000b    |

|        |           | 20120   |           |

|--------|-----------|---------|-----------|

|        | 0000000b  | RCAP2L  | 0000000b  |

| IAPKEY | 0000000b  | SSDAT   | 0000000b  |

| IE     | 0x0x0x00b | SSCON0  | 0000000b  |

| IE1    | xxx00000b | SSCON1  | 0000000b  |

| INTOR  | xxxx000xb | SSCON2  | 0000xx0xb |

| INT2R  | xx00xx00b | TCON    | 0000xx0xb |

| INTOF  | xxxx000xb | TMCON   | xxxxx000b |

| INT2F  | xx00xx00b | TMOD    | x000x000b |

| IP     | xx0x0x00b | тно     | 0000000b  |

| IP1    | xxx00000b | TLO     | 0000000b  |

| OPINX  | 0000000b  | TH1     | 0000000b  |

| OPREG  | nnnnnnb   | TL1     | 0000000b  |

| OTCON  | 00xxxxxb  | T2CON   | 0xxxx0xxb |

| IOHCON | 0000000b  | TH2     | 0000000b  |

| P0     | xx000000b | TL2     | 0000000b  |

| POCON  | xx000000b | WDTCON  | xxx0x000b |

| РОРН   | xx000000b | CHKSUML | 0000000b  |

| P1     | xx000000b | CHKSUMH | 0000000b  |

| P1CON  | xx000000b | OPERCON | xxxxxx0b  |

### 7.4 High-speed RC Oscillator

The SC92F837X has a built-in adjustable high-precision HRC. HRC is precisely calibrated to 24 MHz@5V/25°C when delivery. The user can set system clock as 12/6/2MHz by programmer Code Option. The calibration process is to filter the influence of processing deviation on precision. There will be certain drifting of this HRC depending on operating temperature and voltage. As for voltage drifting (2.9V ~ 5.5V) and temperature drifting (-20°C ~ 85°C), the deviation is within ±1%.

| OP CTM0 | (C1H@FFH) | Customer   | Option | Register 0 | (Read/Write)    |

|---------|-----------|------------|--------|------------|-----------------|

|         | (0@)      | 0401011101 | option | nogiotoi e | (1.0044, 11110) |

| Bit Number      | 7     | 6 | 5          | 4   | 3      | 2      | 1         | 0 |

|-----------------|-------|---|------------|-----|--------|--------|-----------|---|

| Bit<br>Mnemonic | ENWDT | - | SCLKS[1:0] |     | DISRST | DISLVR | LVRS[1:0] |   |

| R/W             | R/W   | - | R/         | R/W |        | R/W    | R/W       |   |

| POR             | n     | х | n          |     | n      | n      | 1         | ſ |

| Bit Number | Bit Mnemonic | Description                                                                                                                                    |

|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 ~ 4      | SCLKS[1: 0]  | System clock frequency selection bits:                                                                                                         |

|            |              | 00: reserved;<br>01: system clock frequency is HRC frequency divided by 2;                                                                     |

|            |              | <ul><li>10: system clock frequency is HRC frequency divided by 4;</li><li>11: system clock frequency is HRC frequency divided by 12;</li></ul> |

The SC92F837X has a special function: the user can modify SFR value to adjust frequency of HRC within certain scope.

#### OP\_HRCR (83h@FFH) System Clock Change Register (Read/Write)

| Bit Number      | 7       | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|---------|--------|---|---|---|---|---|---|

| Bit<br>Mnemonic | OP_HRCR | [7: 0] |   |   |   |   |   |   |

| R/W | R/W |   |   |   |   |   |   |   |

|-----|-----|---|---|---|---|---|---|---|

| POR | n   | n | n | n | n | n | n | n |

| Bit Number | Bit Mnemonic | Description                                                                                                                                                                                                                                                                         |                                                           |  |  |  |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| 7~0        | OP_HRCR[7:0] | HRC frequency change register                                                                                                                                                                                                                                                       |                                                           |  |  |  |

|            |              | OP_HRCR[7:0] the value of HRC after power on ensures that HRC can work at 12/6/2MHz accurately (according to the user's Code Option). The initial value of this value may vary from IC to IC. Users can change the HRC operating frequency by modifying the value of this register. |                                                           |  |  |  |

|            |              | The initial value is OP_HRCR [s]. At this time, IC works at 12/6/2<br>For every 1 change in OP_HRCR [7:0], HRC frequency changes<br>about 0.23%@12MHz.                                                                                                                              |                                                           |  |  |  |

|            |              | The relationship betweer is shown as follows:                                                                                                                                                                                                                                       | n OP_HRCR [7: 0] and output frequency fsys                |  |  |  |

|            |              | OP_HRCR [7:0]                                                                                                                                                                                                                                                                       | HRC actual output frequency<br>(taking 12M as an example) |  |  |  |

|            |              | OP_HRCR [s]-n                                                                                                                                                                                                                                                                       | 12000*(1-0.23%*n)kHz                                      |  |  |  |

|            |              |                                                                                                                                                                                                                                                                                     |                                                           |  |  |  |

|            |              | OP_HRCR [s]-2                                                                                                                                                                                                                                                                       | 12000*(1-0.23%*2) = 11944.8kHz                            |  |  |  |

|            |              | OP_HRCR [s]-1                                                                                                                                                                                                                                                                       | 12000*(1-0.23%*1) = 11972.4kHz                            |  |  |  |

|            |              | OP_HRCR [s]                                                                                                                                                                                                                                                                         | 12000kHz                                                  |  |  |  |

|            |              | OP_HRCR [s]+1                                                                                                                                                                                                                                                                       | 12000*(1+0.23%*1) = 12027.6kHz                            |  |  |  |

Super High-speed 1T 8051-based Touchkey Flash MCU

| OP_HRCR [s]+2                                                                               | 12000*(1+0.23%*2) = 12055.2kHz                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                                                                                                                                                                                                                                                                    |

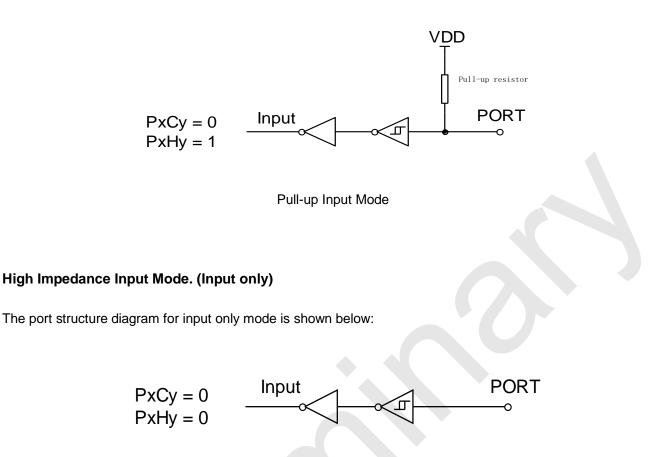

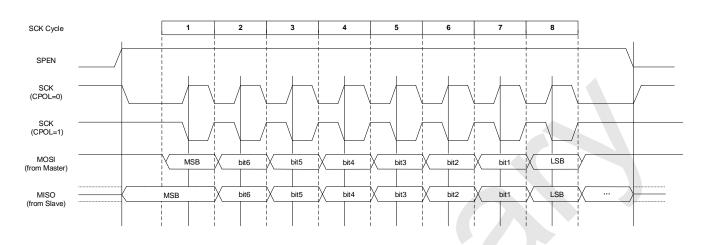

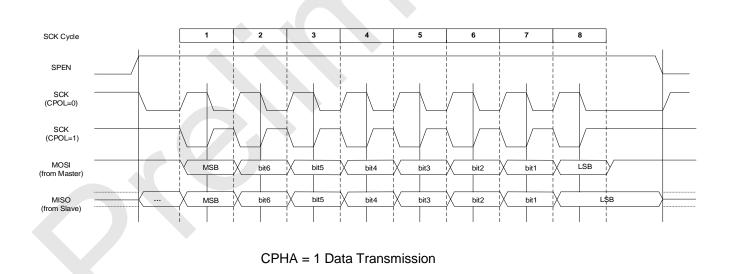

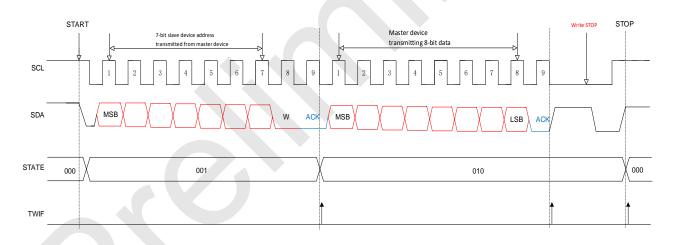

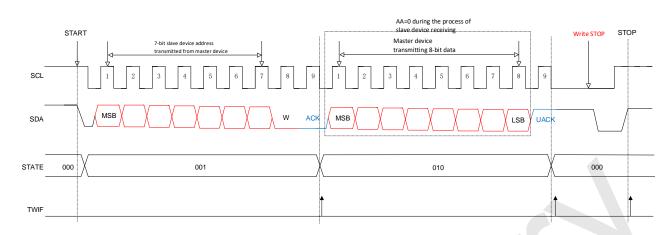

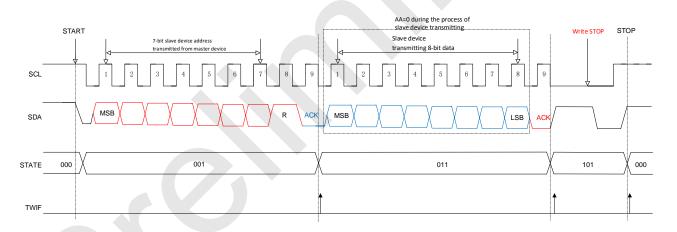

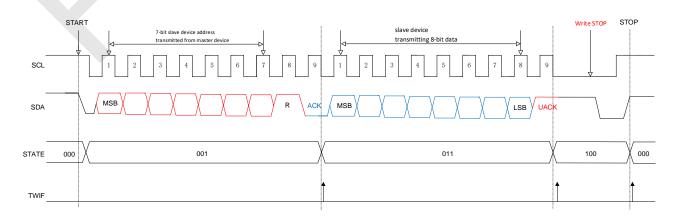

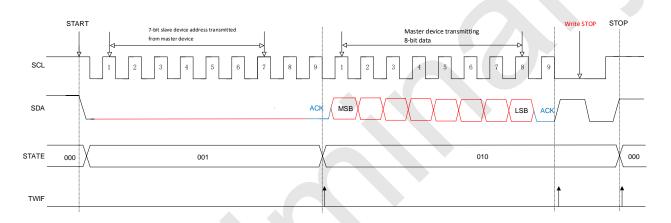

| OP_HRCR [s]+n                                                                               | 12000*(1+0.23%*n)kHz                                                                                                                                                                                                                                               |